MANUFACTURER

EFINIX

レスターは「EFINIX」の代理店です。

破壊的なFPGAプラットフォーム

イノベーションを加速します

Efinixは、2012年にアメリカで設立されたFPGAスタートアップで、今までにはない革新的なQuantum™テクノロジーにより従来のFPGAよりも、4倍のPPA(パワー・パフォーマンス・エリア)を実現しました。Trion FPGAは、この技術により他社FPGAと同性能にもかかわらず、低消費、最適な価格で量産出荷中です。さらに高性能化、高集積化を実現したTitanium FPGAも量産出荷中で順次ラインアップを追加しております。

Efinixの特徴

低消費電力、リコンフィギュラブル、高性能!メインストリーム市場向け FPGA プラットフォーム

EfinixのFPGA のコア技術は、従来の FPGA 技術と比較し、電力、性能、面積の全てにおいて優位性を持つ、革新的なQuantum™ ファブリックです。EfinixのTitanium FPGA は、新たなアプリケーションを開拓し、メインストリーム市場でのイノベーションのための迅速な市場投入を可能にします。4,000 から100 万ロジック・エレメント (LE) までの集積度を持つEfinixのFPGA は、カスタム・ロジック、演算アクセラレーション、機械学習やディープラーニングなど、お客様の次の設計課題に対応する準備が整っています。

Low Power, Small Footprint,

Big Compute

わずか数平方ミリメートルのスペースに、できるだけ多くのコンピューティング能力を詰め込む必要があります。

エフィニックス(Efinix)の次世代Titanium FPGAは16nmプロセスで製造されており、可能な限り低い消費電力と

小さな物理サイズで高いパフォーマンスを実現します。

小型パッケージ

Titanium FPGAは、わずか 3.5mm x 3.4mm WLCSP の極小パッケージを備え、高度に統合されるアプリケーション向けに設計されています。

ハードコントローラー

ハード化されたMIPI D-PHY と DDR DRAMコントローラーは、IoT・温度カメラ・産業用カメラ・ロボティクス・スマートデバイスをサポートします。

SEU保護

Titanium デバイスはデバイスの整合性を監視し、ランダムな SEU イベントからシームレスかつ自動的に回復でき、アプリケーションの稼働時間を最大限に確保します。

ビットストリームの

セキュリティ

ビットストリーム認証は不要な改ざんを防止し、ビットストリーム暗号化は設計の安全性を保証します。

製品寿命

Titanium製品は、多くの多様な市場における幅広い用途に合わせて設計されています。 これらの市場のいくつかは、長期製品ライフサイクルが特徴で、一度大量生産されると、部品表の仕様やコンポーネントの変更に抵抗があります。 Efinixではそれを理解しており、お客様の製品ライフサイクルを通してサポート対象製品を安定的に供給することに尽力しています。 当社は、少なくとも 2045年まで、Titaniumファミリ FPGA をサポートすることをお約束しています。製品ライフサイクルの詳細については、弊社にお問い合わせください。

FGPAラインナップおよびパッケージ

Titanium FPGA Family

※下の表は左右にスワイプすることができます

| 機能 | Ti35 | Ti60 | Ti90 | Ti120 | Ti165 | Ti180 | Ti240 | Ti375 | Ti550 | Ti750 | Ti1000 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| ロジック・ エレメント (LEs) |

36,176 | 62,016 | 92,534 | 123,379 | 162,800 | 176,256 | 236,888 | 370,137 | 550,000 | 750,000 | 1,000,004 |

| 10K メモリブロック (Mb) | 1.53 | 2.62 | 6.88 | 9.18 | 12.1 | 13.11 | 17.62 | 27.53 | 40.92 | 55.8 | 74.4 |

| DSPブロック | 93 | 160 | 336 | 448 | 590 | 640 | 860 | 1,344 | 2,006 | 2,736 | 3,648 |

| PLLs | 4 | 4 | 10 | 10 | 12 | 10 | 12 | 12 | 12 | 12 | 12 |

| GPIO | 34 | 34 | 80 | 80 | 181 | 80 | 181 | 181 | 200 | 200 | 200 |

| 高速 I/O | 146 | 146 | 232 | 232 | 235 | 232 | 235 | 235 | 320 | 320 | 320 |

| LPDDR4/4x | — | — | x32 | x32 | 2x32 | x32 | 2x32 | 2x32 | 2x72 | 2x72 | 2x72 |

| MIPI D-PHY 2.5 Gbps | — | — | 4 RX 4 TX |

4 RX 4 TX |

3 RX 3 TX |

4 RX 4 TX |

3 RX 3 TX |

3 RX 3 TX |

3 RX 3 TX |

3 RX 3 TX |

3 RX 3 TX |

| Tranceivers | — | — | — | — | x16 | — | x16 | x16 | x24 | x24 | x24 |

| 25.8 Gbps Transceivers | — | — | — | — | — | — | — | — | x8 | x8 | x8 |

| Hardened RISC-V block | — | — | — | — | Quad Core |

— | Quad Core |

Quad Core |

Quad Core |

Quad Core |

Quad Core |

| PCIe® Gen4 (16G) | — | — | — | — | 2x4 | — | 2x4 | 2x4 | 2x8 | 2x8 | 2x8 |

Titanium パッケージ オプション

※下の表は左右にスワイプすることができます

| パッケージ | ピッチ (mm) |

サイズ (mm) |

Ti35 | Ti60 | Ti90 | Ti120 | Ti165 | Ti180 | Ti240 | Ti375 | Ti550 | Ti750 | Ti1000 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 64ボール WLCSP | 0.4 | 3.5x3.4 | |||||||||||

| 100ボール FBGA | 0.5 | 5.5x5.5 | |

||||||||||

| 225ボール FBGA | 0.65 | 10x10 | |

||||||||||

| 256ポール FBGA | 0.8 | 13x13 | |

||||||||||

| 361ボール FBGA | 0.65 | 13x13 | |

||||||||||

| 400ボール FBGA | 0.8 | 16x16 | |

||||||||||

| 484ボール FBGA | 0.8 | 18x18 | |

|

|

||||||||

| 529ボール FBGA | 0.8 | 19x19 | |||||||||||

| 676ボール FBGA | 0.8 | 22x22 | |

|

|||||||||

| 900ボール FBGA | 0.8 | 25x25 | |

|

|||||||||

| 1,156ボール FBGA | 1.0 | 35x35 | |

|

詳細情報

低消費電力、大量生産アプリケーション向け、高性能

量産に最適なデバイスが新たなファミリとして登場しました。Topaz FPGAは、非常に効率的なアーキテクチャと、一般的に使用されている

機能やプロトコル (PCIe Gen3、MIPI、LPDDR4、LVDS など) を組み合わせているため、大規模に展開できます。

優れた利用率

XLRセルにさらに多くのロジックを詰め込むように設計された Topazアーキテクチャにより、より機能を実装できるようになりました。

プロトコルサポート

一般的に使用されるプロトコル (LVDS、MIPI、イーサネット、PCIe Gen3) を備えた Topaz FPGAは、マシンビジョン、ロボット工学、プリンターなどのアプリケーションをサポートします。

使いやすいパッケージ

Topaz FPGAは、システムに簡単に統合できる幅広い BGAパッケージを提供しています。

シームレスな移行

デザインのパフォーマンスをアップグレードする必要がある場合や、ロジックを追加する必要がある場合は、Topaz から Titanium FPGA に簡単に移行できます。

製品寿命

Topaz製品は、多くの多様な市場における幅広い用途に合わせて設計されています。 これらの市場のいくつかは、長期製品ライフサイクルが特徴で、一度大量生産されると、部品表の仕様やコンポーネントの変更に抵抗があります。 Efinixではそれを理解しており、お客様の製品ライフサイクルを通してサポート対象製品を安定的に供給することに尽力しています。 当社は、少なくとも 2045 年まで、Topazファミリ FPGA をサポートすることをお約束しています。製品ライフサイクルの詳細については、弊社にお問い合わせください。

FPGAラインナップおよびパッケージ

Topaz FPGA Family

※下の表は左右にスワイプすることができます

| 機能 | Tz50 | Tz75 | Tz100 | Tz110 | Tz170 | Tz200 | Tz325 |

|---|---|---|---|---|---|---|---|

| Logic Elements (LEs) | 52,160 | 75,520 | 101,440 | 120,584 | 172,008 | 215,360 | 326,080 |

| 10K RAM blocks (Mb) | 2.4 | 5.34 | 6.32 | 6.41 | 11.14 | 15.77 | 19.22 |

| DSP blocks | 140 | 264 | 312 | 320 | 544 | 840 | 1008 |

| PLLs | 4 | 12 | 12 | 10 | 10 | 12 | 12 |

| GPIO | 34 | 133 | 133 | 80 | 80 | 181 | 181 |

| High-speed I/O | 146 | 139 | 139 | 232 | 232 | 235 | 235 |

| LPDDR4 | — | 1x32 | 1x32 | 1x32 | 2x32 | 2x32 | 2x32 |

| MIPI D-PHY 2 Gbps | — | 2 RX 2 TX |

2 RX 2 TX |

4 RX 4 TX |

4 RX 4 TX |

3 RX 3 TX |

3 RX 3 TX |

| 12.5 Gbps transceivers | — | x8 | x8 | — | — | x16 | x16 |

| Hardened RISC-V block | — | Quad Core |

Quad Core |

— | — | Quad Core |

Quad Core |

| PCIe® Gen3 (8G) | — | 1x4 | 1x4 | — | — | 2x4 | 2x4 |

Topaz Package Options

※下の表は左右にスワイプすることができます

| Package | Pitch (mm) |

Size (mm) |

Tz50 | Tz75 | Tz100 | Tz110 | Tz170 | Tz200 | Tz325 |

|---|---|---|---|---|---|---|---|---|---|

| 100-ball FBGA | 0.5 | 5.5x5.5 | |||||||

| 225-ball FBGA | 0.65 | 10x10 | |

||||||

| 256-ball FBGA | 0.8 | 13x13 | |

||||||

| 361-ball FBGA | 0.65 | 13x13 | |

|

|||||

| 400-ball FBGA | 0.8 | 16x16 | |||||||

| 400-ball FBGA | 0.5 | 10x10 | |

||||||

| 484-ball FBGA | 0.8 | 18x18 | |

|

|

|

|||

| 529-ball FBGA | 0.8 | 19x19 | |

|

|||||

| 576-ball FBGA | 0.65 | 16x16 | |||||||

| 676-ball FBGA | 0.8 | 22x22 | |||||||

| 676-ball FBGA | 0.65 | 18x18 | |

|

|||||

| 900-ball FBGA | 0.8 | 25x25 |

電力性能領域における利点の実現

この Trion® プラットフォームは SMIC 40nm LL プロセスで製造され、4,000 ~ 12万ロジック・エレメント (LE) のロジック集積度を持ち、GPIO、PLL、発振器、MIPI、DDR、LVDS などの標準インターフェイスを内蔵しています。Trion FPGA は、汎用カスタム・ロジック市場 (モバイル、IoT、一般的なコンシューマ製品、産業機器、医療機器など) をターゲットにしています。また、エッジデバイスでの深層学習や演算アクセラレーターのような急成長している市場もサポートします。

小型パッケージ

Trion FPGAは、わずか 4.5mm x 3.6mm WLCSP の最小パッケージを備え、高度に統合されるアプリケーション向けに設計されています。

MIPI CSI-2 コントローラ

一般的なMIPI CSI-2インターフェイスのハードコントローラーは、IoT、温度カメラ、産業用カメラ、ロボティクス、スマートデバイスをサポートします。

DDR DRAM コントローラ

DDR DRAMハードコントローラーで処理データを保存できます。

製品寿命

Trion製品は、多くの多様な市場における幅広い用途に合わせて設計されています。 これらの市場のいくつかは、長期製品ライフサイクルが特徴で、一度大量生産されると、部品表の仕様やコンポーネントの変更に抵抗があります。 Efinixではそれを理解しており、お客様の製品ライフサイクルを通してサポート対象製品を安定的に供給することに尽力しています。 当社は、少なくとも 2045 年まで、Trionファミリ FPGA をサポートすることをお約束しています。製品ライフサイクルの詳細については、最寄りの営業担当者にお問い合わせください。

FPGAラインナップおよびパッケージ

Trion FPGA ラインナップおよびパッケージ

※下の表は左右にスワイプすることができます

| 機能 | T4 | T8 | T13 | T20 | T35 | T55 | T85 | T120 |

|---|---|---|---|---|---|---|---|---|

| ロジック・エレメント (LEs) | 3,888 | 7,384 | 12,828 | 19,728 | 31,680 | 54,195 | 84,096 | 112, 128 |

| マスク・プログラマブルメモリ (MPM) | — | — | — | — | ||||

| 内蔵メモリビット (kb) | 77 | 123 | 727 | 1,044 | 1,475 | 2,765 | 4,055 | 5,407 |

| 18x18 乗算器 | 4 | 8 | 24 | 36 | 120 | 150 | 240 | 320 |

| PLLs | 1 | 5 | 5 | 7 | 7 | 8 | 8 | 8 |

| LVDS (TX, RX) | — | 6,6 | 13,13 | 20,26 | 20,26 | 52,52 | 52,52 | 52,52 |

| DDR3, LPDDR3, LPDDR2 (up to 1066 Mbps) | — | — | — | x16 | x16 | x32 | x32 | x32 |

| MIPI DPHY (4レーン) 内蔵 MIPI CSI-2 コントローラ | — | — | 2 RX 2 TX |

2 RX 2 TX |

2 RX 2 TX |

3 RX 3 TX |

3 RX 3 TX |

3 RX 3 TX |

Trion パッケージ オプション

※下の表は左右にスワイプすることができます

| パッケージ | ピッチ (mm) |

サイズ (mm) |

GPIO (1) |

PLLs | SPI Flash (Mbit) |

LVDS Pairs TX,RX |

MIPI CSI-2 TX,RX(1) | DDR DRAM(1) |

T4 | T8 | T13 | T20 | T35 | T55 | T85 | T120 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 49ボール FBGA | 0.4 | 3x3 | 33 | 1 | ||||||||||||

| 80ボール WLCSP | 0.4 | 4.5x3.6 | 33 | 3 | 1,1 | |||||||||||

| 81ボール FBGA | 0.5 | 5x5 | 55 | 1 | ||||||||||||

| 100-pin LQFP | 0.5 | 14x14 | 65 | 5 | 16 | 4,4 | ||||||||||

| 144-pin LQFP | 0.5 | 20x20 | 97 | 5 | 6,6 | |||||||||||

| 169ボール FBGA | 0.65 | 9x9 | 73 | 5 | 8,12 | 2,2 | |

|||||||||

| 256ボール FBGA | 0.8 | 13x13 | 195 | 5 | 13,13 | |||||||||||

| 324ボール FBGA | 0.65 | 12x12 | 130 | 7 | 20,26 | 2,2 | x8,x16 | |

|

|

|

|||||

| 400ボール FBGA | 0.8 | 16x16 | 230 | 7 | 20,26 | x8,x16 | ||||||||||

| 484ボール FBGA | 0.8 | 18x18 | 256 | 8 | 40,40 | x16,x32 | |

|

|

|||||||

| 576ボール FBGA | 0.65 | 16x16 | 278 | 8 | 52,52 | 2,2 | x16,x32 | |

|

|

(1) MIPI および DDR インターフェイスは専用の I/O を使用しますので、最大 GPIO 本数は、それらのインターフェイスの I/O 数を含みません。

詳細情報

Simple,Easy-to-Use Toolflow

エフィニックス (Efinix®) の Efinity® は RTL デザインからビットストリーム生成までの完全なツールフローを提供します。シンプルで使いやすい GUI インターフェイスとコマンドライン スクリプトをサポートし、Titanium、Trion® FPGA のデザインに必要なツールが全て含まれています。

Efinity ソフトウェアをダウンロード - 無料

Efinixは、Efinityソフトウェアを無料でライセンス提供します。 また、開発キットを購入すると、ソフトウェアライセンスと 1年間のアップグレードも提供されます。 最初の1年後は、無料のメンテナンス更新をリクエストできます。 あなたが入手するバージョンは、機能を簡素化した Web エディションではなく、EfinixのすべてのFPGAをサポートしています。

無料ライセンスを取得するには、Efinix公式HPのサポートセンターに登録してください。 次に、Efinityページをクリックして無料ライセンスをリクエストします。 ライセンスと1年間のメンテナンス (アップグレードおよびパッチ) が 1年間提供されます。 さらに 1年間のメンテナンスをいつでも無料でリクエストできます。

-v2024.1の新機能

EfinityソフトウェアV2024.1には、次の新機能と拡張機能があります

- Titanium FPGAのトランシーバーサポートを導入

-PCI Express Gen4x4 をサポート

-Ethernet 10GBase-KR をサポート - 新しいデバイスサポート: Ti375 N1156 および N484パッケージ、Ti240およびTi165のFPGA

- Ti35およびTi60 F256パッケージとTi60 FPGAのビットストリームサポートを追加

- タイミング解析用のTclスクリプトの改善

- Titanium設計のコンパイル時間の改善

- トランシーバーのデバッグと解析を支援する新しい Efinity Transceiver Debuggerツール

- IPマネージャーで使用するために設計ファイルをスタンドアロン IPとしてパッケージ化する新しい IP Packagerツール

- トランシーバー ブロック用の Python APIの更新

キットを使って始める

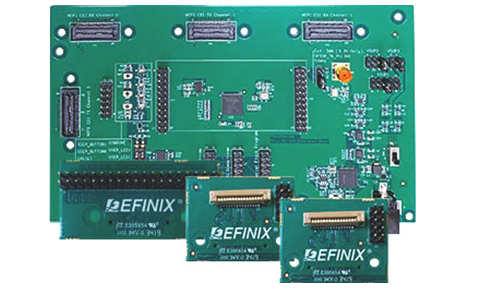

Efinixの開発キットは、Efinix FPGA を使用した設計を迅速に開始するのに役立ちます。 各キットとともに、Efinity® ソフトウェアのライセンスも受け取ります。 Efinix では、キットに含まれているカード以外にもいくつかのドーターカードを個別に提供しています。

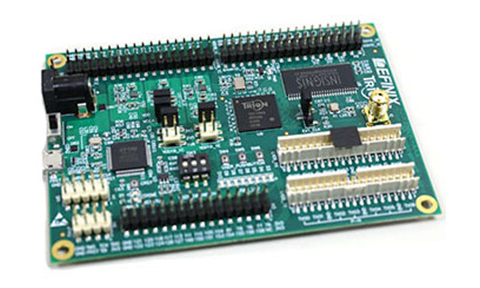

-Titanium Ti375 PCIe® Early Access Board

このアーリーアクセス ボードは、Ti375 FPGA と PCIe Gen4 x4 機能を実現したEfinixの最初のボードです。実際にTi375 PCIe トランシーバーの動作を確認できます。

-Titanium Ti375 C529開発キット

この開発キットを使用すると、最大1 Gbpsまでのクロック周波数で動作できるTi375 FPGAのハード化されたクアッドコアRISC-Vプロセッサの機能を開発できます。

-Titanium Ti180 J484 C529開発キット

Ti180 J484開発キットは、レーンあたり最大 2.5 Gbps をサポートする Ti180 FPGA のハード化された MIPI D-PHY とハード化された LPDDR4x コントローラーを紹介します。

-Titanium Ti60 F225開発キット

Ti60 FPGA、Raspberry Pi カメラ、DSI ディスプレイなど、ビジョンシステムのプロトタイプに必要なものがすべて揃っています。

MIPI CSI-2用キット

Efinixの Trion FPGA の一部は、ハード化された MIPI CSI-2ブロックを備えており、優れたカメラセンサーインターフェイスと画像処理に十分なロジックを提供します。 ハード DDR DRAM メモリコントローラは、フレームバッファまたはその他のシステムメモリに接続できます。 Efinixの MIPI CSI-2 ベースの開発キットは Raspberry Pi やその他のカメラに接続できるため、ビジョンアプリケーションのプロトタイプを簡単に開発できます。

-Trion T120 BGA576 開発キット

この T120 キットは BGA576 パッケージを特徴とし、より多くの I/O、LPDDR3 メモリ、ユーザー入力、および PMODコネクタを備えており、完全なシステムのプロトタイプを作成するために必要な機能を提供します。

-Trion T120 BGA324 開発キット

T120 FPGA MIPI CSI-2 および DDR DRAMコントローラーを使用するプロトタイプデザイン。 ビデオを処理して HDMIコネクタを使用してディスプレイに送信し、PMODコネクタを使用してカスタム周辺機器を接続します。

-Trion T20 MIPI 開発キット

T20 FPGA を備えたスターター MIPI CSI-2 開発キット。 このキットには、MIPIカメラやその他の外部デバイスに接続したり、GPIOを拡張したりできる 3 つのドーターカードが付属しています。

I/O拡張キット

Efinixの I/O 拡張キットは、ボード上のコネクタとヘッダーを介して I/O にアクセスできるようにします。 これらのボードには、LED とスイッチに加えて、もう 1つボード上にクロックオシレーターもあります。 ヘッダーとコネクタを介して他のボードに接続したり、スタンドアロンで使用して処理機能を実証したりできます。

-Trion T20 BGA256 開発キット

I/O breakout board featuring the T20 BGA256 FPGA

-Trion T8 BGA81 開発キット

Starter board featuring the T8 BGA81 FPGA.

詳細情報

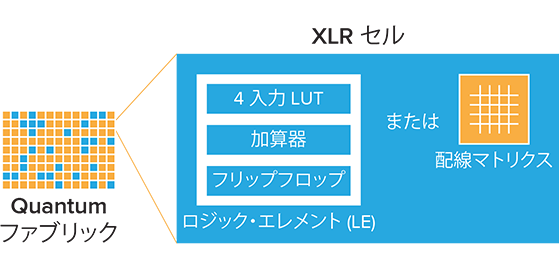

シリコン製品に最高の電力、性能、面積 (サイズ) を提供するため、エフィニックス (Efinix) は、プログラマブル・テクノロジをリードする

Quantum® アーキテクチャを設計しました。当社の目標は、機械学習、ディープラーニング、高速演算アクセラレータなどの

計算集約型アプリケーションに合わせた、最も柔軟性の高いプログラマブル・テクノロジを提供することです。

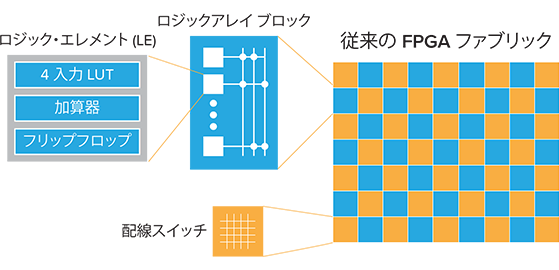

切り替え可能なロジックおよびルーティング (XLR) セル

Quantum® ファブリックの基本的な構成要素は、切り替え可能なロジックおよびルーティング (XLR) セルです。 XLR セルは、LUTベースのロジックセルとして機能し、スケーラブルで柔軟なルーティング構造で変換されたルーティングスイッチとして機能します。 ソフトウェアがXLRセルをロジックか配線かどうかを決めます。 専用ロジックと専用配線を持つことは、良いアイデアのように思えます。ほとんどの複雑な論理ブロックには、ブロックへの入出力信号が多数あります。すべての入出力信号を使い切ると、ブロック内の残りのロジックにアクセスできなくなります。 任意の XLRセルを配線にできるため、ソフトウェアは混雑を回避し最適なパスを選択できます。

XLRセルの利点

- 微細なアーキテクチャ

- 無駄のないインターフェイス

- ロジックと配線の柔軟な構成

- 接続性の高いインターコネクト

- ハイブリッド配置配線アルゴリズム

- すべてCMOSパスゲート

- 標準的なシリコン製造手法

従来のFGPAと第一世代Quantum®ファブリックの比較

従来のFPGAは、論理素子と配線リソースの固定された比率で設計されています。 配線リソースが少なすぎると論理素子を接続できず、FPGAが十分に活用されないため、この比率は非常に重要です。 配線リソースが多すぎるとシリコン領域が無駄になり、チップ単価に反映されます。

XLRセルのおかげで、Efinix® FPGA は従来の FPGA よりもより小さく、消費電力が低く、効率が高くなります。 また、従来の FPGA とは異なり、Efinix® FPGA は標準の CMOSシリコンプロセスで製造されています。 標準プロセスを使用すると、我々のFPGA は生産が容易になり、大量生産を最適化できます。

- 面積が 1/2 ~ 1/4 に削減可能

- 消費電力が 1/2 以下に

- 100 万 LE 以上まで拡張可能

- ワイドなデータバスが構成可能

- データのパイプライン化が容易

- シリコン プロセスに依存しない

Quantum®コンピューティング・ファブリックによるレベルアップ

第二世代 Quantum® コンピューティング・ファブリックは、さらに多くの演算処理および柔軟な配線を実現すべく、高効率化した XLR セルに加え、10Kのメモリブロックと高機能の DSP ブロックが追加されています。

Quantumコンピューティング構造は、構成可能なタイル、切り替え可能なロジックおよび配線 (XLR) セルで構成されており、高い使用率を達成しながら配線効率と速度を最適化します。 この構造にはまた、高度に構成可能な組み込みメモリブロックと、専用の高速 DSP ブロックも備えています。 これらの機能を組み合わせることで、エッジコンピューティングから産業オートメーションやビデオ処理まで、幅広いアプリケーションに最適なパフォーマンスを提供します。

- 16 nm プロセス

- 第一世代からクロック周波数を 3 倍に

- 第一世代から 2 倍の高効率化

- 極小のダイサイズ

- 低消費電力

コンフィギュレーションに関して

Efinix FPGAのコンフィギュレーションモード

Efinix FPGAのコンフィギュレーションモードは大別すると以下の3つとなります。

コンフィギュレーションモード

| Mode | 説明 |

|---|---|

| SPI Active | FPGAがSPI MasterとなるMode。外付けでSPI Flashを接続しFPGAがSPI通信でbit streamを読み出しコンフィギュレーションします。 |

| SPI Passive | FPGAがSPI SlaveとなるMode。外付けマイコン等のSPI MasterデバイスからFPGAへbit streamを流し込むことによりコンフィギュレーションします。 |

| JTAG | ホストコンピュータなどからJTAG I/Fへbitstreamを流し込むことによりコンフィギュレーションします。主にデバッグ時などに使用します。 |

技術資料

Efinity紹介

Efinix FPGAの統合開発環境であるEfinityの説明です。これからEfinityを使おうとする方。Efinityを使い始めたばかりの方に Efinityの操作方法などを説明しています。

Efinity Interface Designer GPIO,JTAG,PLL設定

Interface designerは Efinix社 FPGAをデザインする上でハードマクロの定義・設定などを行う機能です。 論理開発(HDL)でないハードマクロは Interface designerで定義を行います。 本編では、GPIO, PLL, JTAG の設定方法を説明します。

Efinix FPGA JTAG SPI Flash Loader

JTAG SPI Flash LoaderはビットストリームデータをJTAGから入力。FPGAをスルーさせSPI Flashへ書き込みを行なうIPです。SPIのコネクタを実装せずにFlashへの書き込みを実現できます。

Efinity Debugger Logic Analyzer

Efinix FPGAのデバッグ手法を解説します。開発環境Efinityを使ったデバッグインスタンス生成~実行までの手法を解説します。

カタログ