Efinix FPGA Configuration

FPGAコンフィギュレーション講習

Efinix FPGAのコンフィギュレーションモード

Efinix FPGAのコンフィギュレーションモードは大別すると以下の3つとなります。

コンフィギュレーションモード

| Mode | 説明 |

|---|---|

| SPI Active | FPGAがSPI MasterとなるMode。外付けでSPI Flashを接続しFPGAがSPI通信でbit streamを読み出しコンフィギュレーションします。 |

| SPI Passive | FPGAがSPI SlaveとなるMode。外付けマイコン等のSPI MasterデバイスからFPGAへbit streamを流し込むことによりコンフィギュレーションします。 |

| JTAG | ホストコンピュータなどからJTAG I/Fへbitstreamを流し込むことによりコンフィギュレーションします。主にデバッグ時などに使用します。 |

コンフィギュレーション(デバッグ)ツール

Efinixでは純正のデバッグツールは用意されておりませんが、ISX社よりEfinix FPGAをターゲットとしたデバッグ ツールがリリースされています。

レスターでは、同製品を取扱っておりますので、ご質問等ございましたらお問い合わせください。

デバッグツールのデバイスドライバー

Efinixでは純正のデバッグツールは用意されていませんが、ISX社よりEfinix FPGAをターゲットとしたデバッグ ツールがリリースされています。

Windows標準のデバイスドライバーではISX社デバッグツールやEfinix社FPGA評価ボードを認識することができません。このためデバイスドライバーの置き換えが必要となります。

準備:

デバイスドライバーを置き換えるためのツール ‘Zadig’をダウンロードします。

Zadig - USB driver installation made easy (akeo.ie)

実行:

Zadigを実行します。

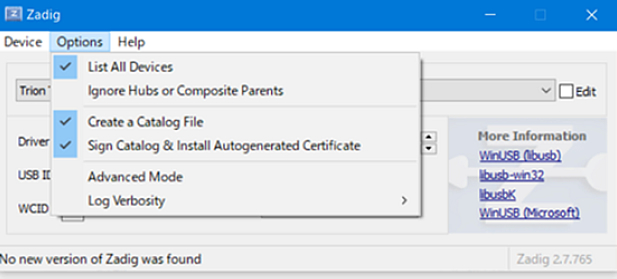

Zadigが起動したら‘Option’ -> ‘List All Devices’を選択。‘Ignore Hubs or Composite Parents’は非選択に。

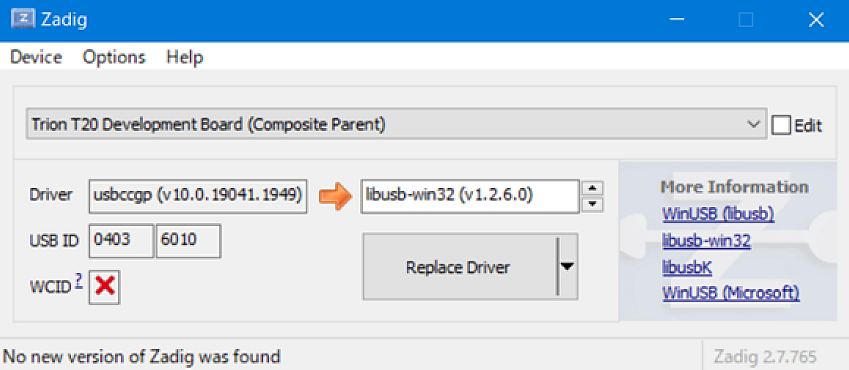

ターゲットデバイスを選択し(図の例ではT20評価ボード)ドライバーをlibusb-win32(v2.6.0)にしてReplace Driverボタンを押す

→デバイスドライバーが置き換わり、デバッグツールを認識するようになります。

コンフィギュレーション用のデータをFlash ROMに事前に書き込んで実装する

量産時においては、あらかじめROMにコンフィギュレーションデータを書き込んで実装するケースが多くあります が、書き込みデータフォーマットの主流はIntel Hexまたはbinaryとなります。

一方、コンフィギュレーション用に生成されるbit streamは .bit形式と .hex形式であるので変換が必要となります。

Binaryへの変換方法

(1) Programmerを起動

(2) Bit streamファイル(.hex)を選択

(3) メニューの’File’ -> ‘Export’を選択

(4) ファイルの種類で’Raw Binary’を選択しファイル名を入力でBinaryが生成

Intel Hexへの変換方法

(1) Efinity実行ディレクトリへ移動(例;'c:\Efinity\2022.2\bin')

例;New_Design.hex'を → 'Intel_New_Design.hex' へ変換する。

(2) 'python3 C:\Efinity\2022.2\pgm\bin\efx_pgm\export_bitstream.py hex_to_intelhex New_Design.hex Intel_New_Design.hex'

(コマンドが長いため、表示は折り返していますが、実際には改行せず実行する。)

(3) 'Successfully wrote Intel_New_Design.hex' とコマンドプロンプト表示され変換終了

詳細は、AN 006: Configuring Trion FPGAs (efinixinc.com) または、AN 033: Configuring Titanium FPGAs (efinixinc.com) を参照ください。

JTAG SPI Flash Loader

JTAG SPI Flash LoaderとはBit Streamデータ (.hex) をJTAGから入力、SPIに出力=スルーさせるデザイン

→SPIのコネクタを実装することなくSPI Flashへの書き込みを実現します。

【ユーザーガイド】

JTAG SPI Flash Loader Core User Guide (efinixinc.com)

Bit Streamデータに関して

コンフィギュレーションにて使用される bit stream データは *.bit, *.hexの2種類があります。

*.bit -JTAG I/Fを介してコンフィギュレーションする際に使用するファイルです。

*.hex -SPI Active / Passive modeにてコンフィギュレーションを行なう際に使用するファイルです。

コンフィギュレーションが正常にできない場合の確認事項

コンフィギュレーションを正常に動作させるには、コンフィギュレーションピンのデザイン、接続状態を所定の状態にしたうえで正しい電源シーケンスでの起動することが必要です。

デザインが所望のコンフィギュレーションモードに適合しているかを下記ページにてご確認いただけます。

Trion Hardware Design Guidelines | Efinix (efinixinc.com) または、Titanium Hardware Design Guidelines | Efinix (efinixinc.com)

ISX社のツールを用いてのJTAG SPI Flash Loader プログラム

Q : ISX社のツールを使って JTAG SPI Flash Loader IPを利用したSPI Flash ROMへの書き込みを行なおうとしたところ ’ Invalid flash device. Flash load abort.’ というエラーメッセージが出て、Flash ROMへの書き込みができません。

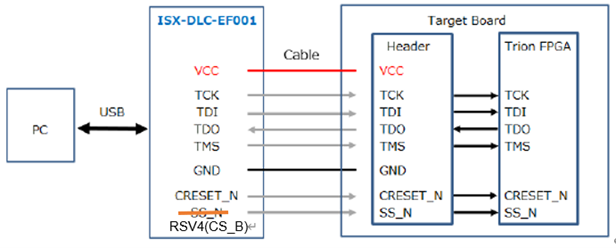

A : Efinity Programmerの仕様変更によるものです。新しいバージョンのProgrammerでは下図のように接続してください。

※ISX社のデータシートではSS_Nを接続となっているところをRSV4(CS_B)接続へ変更

対象となるデバイスはT4F81, T8F81, T8Q144, T13F169, T13F256, T20F169, T20F256。

EFINIX

FPGA

Efinixは、2012年にアメリカで設立されたFPGAスタートアップで、今までにはない革新的なQuantum™テクノロジーにより従来のFPGAよりも、4倍のPPA(パワー・パフォーマンス・エリア)を実現しました。

Trion FPGAは、この技術により他社FPGAと同性能にもかかわらず、低消費、最適な価格で量産出荷中です。さらに高性能化、高集積化を実現したTitanium FPGAは2021年より出荷予定です。